Decodificarea memoriei

În cadrul acestei lucrări se vor prezenta modurile de decodificare a memoriei, cu particularizarea pentru microprocesorul Z80.

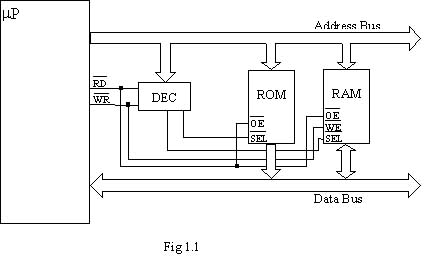

Cel mai simplu sistem cu microprocesor este prezentat în figura 1.1. Acest sistem cuprinde pe lângă procesor, un bloc de memorie fixă (ROM), un bloc de RAM şi decodificatorul de memorie pentru blocurile de memorie existente. Orice circuit de memorie sau bloc de memorie are nevoie de un semnal de selecţie pentru a putea răspunde procesorului la operaţia cerută. Fiecare din aceste semnale de selecţie este o ieşire din decodificatorul de memorie.

Prin generarea semnalelor de selecţie pentru memorii se înţelege obţinerea acelor semnale care activează sau validează circuitele de memorie partenere procesorului.

În continuare se vor prezenta paşii necesari în realizarea unui decodificator de memorie.

Prima problemă pe care trebuie să o rezolve proiectantul, legat de memorie, este stabilirea hărţii memoriei, adică alocarea fiecărui circuit de memorie a cel puţin unei zone din spaţiul direct adresabil al procesorului. Dimensiunea unei asemenea zone este legată de capacitatea circuitului de memorie. Această alocare se face în funcţie de cerinţele unităţii centrale, ale sistemului de operare şi ale aplicaţiei.

Exemplul 1.1:

Când se construieşte harta memoriei trebuie stabilite următoarele două date pentru fiecare circuit (bloc) de memorie:

Adresa de început a unui circuit de memorie se stabileşte în funcţie de:

Exemplul 1.2:

Stabilirea adresei de început pentru un circuit DRAM (RAM dinamic) de 16Ko. Microprocesorul Z80 porneşte după RESET de la adresa 0000h, deci la această adresă ar trebui să existe memorie ROM şi nu putem plasa aici memoria noastră DRAM. Circuitul având capacitatea de 16Ko = 214 poate fi plasat (pentru o decodificare simplă) începând cu adresele 0000h, 4000h, 8000h sau C000h.

Limitele de adresare pentru un circuit se stabilesc în funcţie de capacitatea circuitului:

Există mai multe tehnici pentru generarea semnalelor de selecţie a circuitelor de memorie. De obicei blocul de circuite care generează aceste semnale se numeşte decodificator de adrese de memorie şi are ca intrări linii din magistrala de adrese şi eventual semnale de comandă generate de către procesor.

Adresarea liniară

Adresarea liniară constă în selectarea circuitelor sau blocurilor de memorie utilizând o singură linie din magistrala de adrese.

Exemplul 1.3:

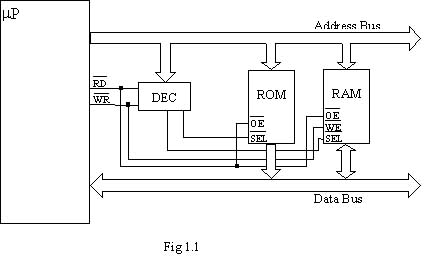

Se cere să se asigure selecţia a două blocuri de memorie (fig 1.2):

|

|

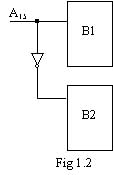

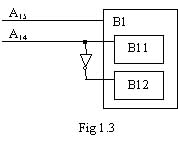

Metoda se poate aplica în continuare (pentru mai multe blocuri) în felul următor: Blocul 1 se împarte la rândul lui în două alte subblocuri (fig 1.3):

Blocul B1

Această metodă este foarte simplă şi presupune puţine circuite, însă se foloseşte doar în cazul unui număr mic de blocuri de memorie, ale căror adrese diferă printr-un număr mic de biţi (1, 2).

Decodificarea completă

Se construieşte un tabel (Tabelul 1.1) care are ca şi coloane rangurile magistralei de adrese iar ca linii prima şi ultima configuraţie de adresă din fiecare zonă acoperită de un circuit. Apoi pentru fiecare zonă se inspectează coloanele pornind de la rangul cel mai semnificativ spre cel mai puţin semnificativ şi se reţin acele ranguri (coloane) care rămân nemodificate pentru orice configuraţie de adresă din zona respectivă. O funcţie logică combinaţională de aceste ranguri va individualiza zona respectivă şi va genera semnalul de selecşie pentru circuitul care acoperă zona respectivă.

Exemplul 1.4:

Să se realizeze selecţia pentru următoarele blocuri de memorie:

|

A15 |

A14 |

A13 |

A12 |

A11 |

A10 |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Tabelul 1.1

Decodificare incompletă

În cadrul decodificării incomplete se construieşte acelaşi tabel ca la decodificare completă, se face aceeaşi inspecşie, dar nu se iau în considerare toate rangurile care individualizează zona respectivă. Aceasta duce la simplificarea decodificatorului, însă un acelaşi circuit va acoperi (va fi văzut în) mai multe zone din spaţiul de adresare al procesorului. Dacă se ignoră un rang din zona ocupată, un circuit va ocupa două zone egale cu capacitatea sa, dacă se ignoră două ranguri, circuitul va ocupa patru zone, etc.

Exemplul 1.5:

În Exemplul 1.4 linia A15 nu este decisivă în selecţia blocurilor de memorie. Dacă se renunţă, în decodificare, la linia A15 din magistrala de adrese toate cele patru circuite de memorie se vor “vedea” în două zone distincte de adrese. Astfel vom avea:

Chiar dacă linia A10 nu rămâne neschimbată pentru toate liniile tabelului, ea nu este indispensabilă selecţiei blocului B1, deci dacă se renunţă şi la linia A10 blocul de memorie B1 se va vedea în patru zone din spaţiul de adresare al procesorului:

Întrucât pe magistrala de adrese circulă mai multe tipuri de informaţii (adrese de porturi, adrese de memorie, registre), există riscul ca atunci când procesorul doreşte să selecteze un port a cărui configuraşie de adresă coincide cu a unei locaţii de memorie, să se selecteze pe lângă port şi circuitul respectiv de memorie. Pentru a evita această situaşie se utilizează ca intrări în decodificatorul de adrese semnale de comandă generate de procesor care să individualizeze fie comunicaţia cu memoria fie cu porturile de intrare/ieşire.

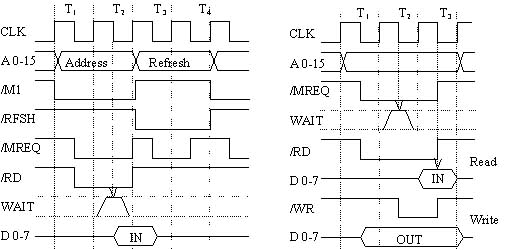

În proiectarea unui decodificator pentru memorie trebuie consultate şi diagramele de timp atât ale microprocesorului cât şi ale memoriilor folosite. Aceasta, în primul rând, pentru a nu exista neconcordanţe de timp între generarea semnalelor de selecţie şi timpii de răspuns a memoriilor. Astfel, dacă o memorie este prea lentă pentru un anumit procesor, ea nu va reuşi să plaseze pe magistrala de date informaţia stocată şi procesorul va citi nişte date invalide. În acest caz trebuie prevăzut un bloc cu logică suplimentară pentru generarea unui semnal de “aşteptare” (la Z80 este WAIT), pentru ca procesorul să aştepte până când memoria poate plasa datele pe magistrală (la fel şi pentru scriere). Acest semnal de aşteptare se poate genera doar pentru blocurile de memorie lente, iar pentru cele mai rapide nu se va activa.

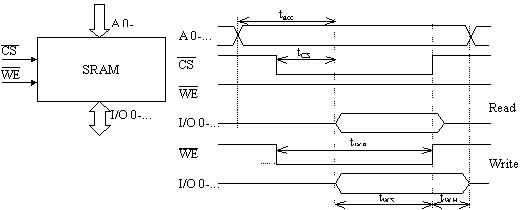

Un al doilea motiv pentru care trebuie luate în calcul şi diagramele de timp este necesitatea respectării ordinii de generare a semnalelor pentru o anumită operaţie cu memoria. De exemplu în cazul unei scrieri în SRAM (2114) este nevoie ca semnalul /WE să se activeze înaintea semnalului /CS.

Pentru aceasta vom prezenta în continuare diagramele de timp ale memoriilor folosite în cadrul laboratorului.

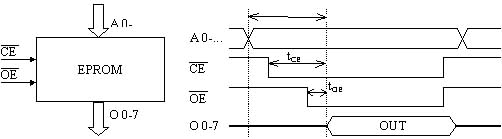

EPROM

Fig 1.4

Pentru circuitul EPROM 2716 (2Ko) avem următorii timpi:

RAM static

Fig 1.5

Pentru circuitul 2114 (1K x 4biţi) avem:

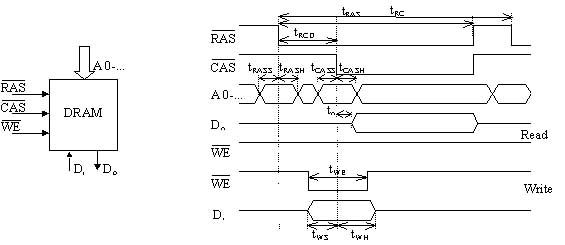

RAM dinamic

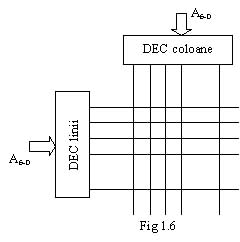

Deoarece memoriile dinamice au capacităţi de stocare mari, şi pentru a nu mări numărul de intrări de adrese s-a recurs la multiplexarea liniilor de adrese, reducându-se la jumătate numărul acestora. O jumătate din liniile de adrese sunt trimise la început şi sunt considerate a fi adresa de linie pentru locaţia dorită. Acestea sunt urmate de cealaltă jumătate de linii, care adresează coloana locaţiei de memorie.

La activarea liniei RAS, memoria preia informaţia de pe liniile A6-0 şi o consideră ca fiind adresa de linie a celulei de memorie; apoi o logică externă trebuie să modifice configuraţia de la intrările A6-0 şi să activeze linia CAS, memoria preluând adresa la activarea lui CAS, o consideră a fi adresa de coloană a celulei de memorie. Celula de memorie astfel selectată va fi încăracată cu o nouă valoare în cazul unei scrieri sau îşi va depune informaţia pe magistrala de date pentru a fi preluată de către procesor, în cazul unei citiri (Fig 1.6).

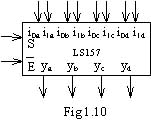

Pentru comutarea adreselor de linie cu cele de coloană se foloseşte un circuit multiplexor (74LS157) extern memoriei ce va fi prezentat în continuare.

Specificul memoriilor RAM dinamice este că ele trebuie reîmprospătate. Circuitul cere ca la maximum 2ms să fie reîmprospătate toate locaţiile. Există facilitatea de reîmprospătare pe linie, adică reîmprospătarea se poate face nu numai la nivel de celulă ci şi la nivel de linie. Pentru aceasta circuitul cere activarea liniei RAS şi plasarea pe A6-0 a adresei de linie.

Fig 1.7

Ciclurile masină (fetch, read, write)

Operaţiile în care procesorul accesează memoria sunt cele de aducere cod instrucţiune (fetch) şi citirea/scrierea din memorie. În figurile 1.8 şi 1.9 sunt prezentate ciclurile de fetch şi citire/scriere din memorie pentru microprocesorul Z80. Frecvenţa de tact la care lucrează microprocesorul Z80 este între 2.5 MHz şi 6 MHz.

Fig. 1.8

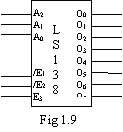

Implementarea decodificatorului de memorie se poate realiza folosind porţi logice (AND, OR, XOR, NOT) circuite decodificatoare (LS 138). Întârzierile pe porţile logice se consideră de aproximativ 10 ns iar pe un circuit decodificator de 30 ns.

Decodificatorul LS138

Circuitul LS138 este un decodificator cu trei intrări de selecţie (A2-A0) şi trei intrări de validare (E3-E1). Acest circuit poate fi folosit în decodificarea memoriei pentru reducerea numărului de circuite logice folosite.

|

E1 |

E2 |

E3 |

A2 |

A1 |

A0 |

O0 |

O1 |

O2 |

O3 |

O4 |

O5 |

O6 |

O7 |

|

1 |

x |

x |

x |

x |

x |

z |

z |

z |

z |

z |

z |

z |

z |

|

x |

1 |

x |

x |

x |

x |

z |

z |

z |

z |

z |

z |

z |

z |

|

x |

x |

0 |

x |

x |

x |

z |

z |

z |

z |

z |

z |

z |

z |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Tabelul 1.2

Multiplexorul LS157

Circuitul LS157 este un multiplexor având opt intrări şi patru ieşiri. Intrările i0i şi i1i sunt multiplexate în funcţie de semnalul S pe ieşirea yi. Circuitul se foloseşte la multiplexarea intrărilor de adrese pentru memoria RAM dinamică.

yi = /E ( I1i S + Ioi /S)

Să se proiecteze decodificatorul de memorie al unui sistem cu microprocesorul Z80 ce conţine următoarele resurse:

Pentru realizarea lucrării se vor urma paşii: