În cadrul acestei lucrări de laborator se vor prezenta generarea codului maşină pentru o secvenţă de program scrisă în limbaj de asamblare şi vizualizarea ciclurilor maşină ale microprocesorului Z80.

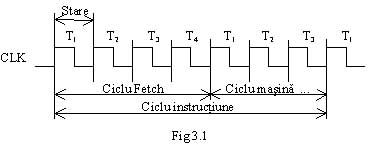

Întreaga activitate a microprocesorului se desfăşoară într-o succesiune de cicluri maşină. Execuţia unei instrucţiuni înseamnă execuţia unei succesiuni de cicluri maşină. Un ciclu maşină este divizat în stări, o stare fiind definită ca o perioadă a tactului. Numărul de stări al unui ciclu maşină diferă în funcţie de tipul ciclului şi funcţie de caracteristicile de timp ale circuitelor de memorie şi porturi. Lungimea minimă a unui ciclu este de 3 stări. Un ciclu maşină poate fi prelungit prin înserarea de stări de WAIT.

Tipurile de cicluri pe care le poate executa Z80 sunt următoarele:

Primul ciclu maşină al oricărei instrucţiuni este un ciclu de fetch (Fig 3.1), prin care se aduce din memorie codul instrucţiunii ce urmează a fi executată. În următoarele cicluri, Z80 poate efectua transferuri de date cu memoria externă sau dispozitivele periferice, în funcţie de tipul instrucţiunii ce a fost decodificate în ciclul precedent de fetch.

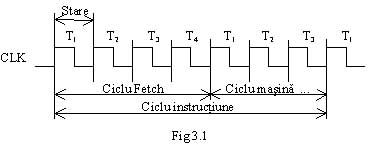

După cum se poate observa şi în figura 3.2 acest ciclu maşină este format din patru stări, fiind împărţit în două subcicluri. În primele două stări se aduce efectiv codul instrucţiunii, iar în următoarele se execută un subciclu de refresh.

Activarea semnalului /M1 indică faptul că se aduce cod de instrucţiune, iar /MREQ că se face acces la memorie. Deoarece codul de instrucţiune este citit din memorie se activează semnalul /RD. Procesorul testează pe frontul posterior al tactului în starea T2 linia WAIT, iar dacă este pe 1 logic continuă ciclul. La începutul stării T3 se face preluarea datelor de pe liniile de date. În următoarele două stări se execută un subciclu de refresh prin plasarea pe magistrala de adrese a conţinutului registrului R şi prin activarea semnalelor /RFSH şi /MREQ. Tot în stările T3 şi T4 se realizează decodificarea şi execuţia instrucţiunii citite.

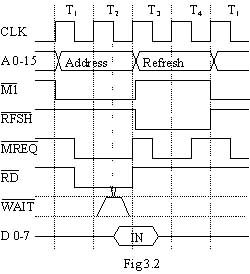

Ciclul de citire (Fig 3.3) se întinde pe durata a trei stări. Activarea semnalelor /MREQ şi /RD indică faptul că se face acces de citire din memorie. Datele sunt preluate de către procesor pe frontul căzător din starea a treia. Procesorul testează pe frontul posterior al tactului în starea T2 linia WAIT, iar dacă este pe 1 logic continuă ciclul. Pentru memoriile mai lente se poate activa linia WAIT ceea ce va determina procesorul să introducă o stare suplimentară.

La fel ca şi ciclul de citire din memorie şi ciclul de scriere în memorie se întinde pe durata a trei stări. Procesorul plasează informaţiile pe magistrala de date încă din prima stare. Dacă pe frontul posterior al lui T2 intrarea WAIT este “1” atunci ciclul continuă, iar în caz contrar se vor introduce stări suplimentare de aşteptare. Singura deosebire constă în activarea semnalului /WR mai târziu cu o perioadă de tact decât semnalul /RD în ciclul de citire.

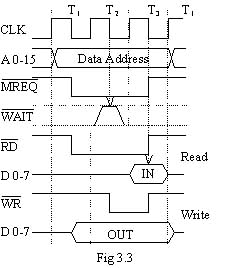

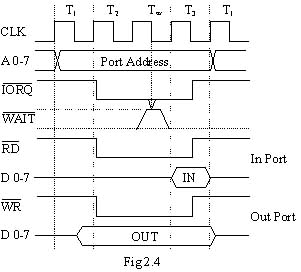

Figura 3.4 ilustrează modul de funcţionare al microprocesorului Z80 în timpul operaţiilor de intrare/ ieşire. Pe durata acestor operaţii Z80 introduce în mod automat o stare Tw, după T2, pentru a permite dispozitivului periferic adresat să-şi decodifice adresa.

Totalitatea instrucţiunilor pe care un microprocesor le poate recunoaşte şi executa, formează setul de instrucţiuni al microprocesorului respectiv.

O instrucţiune este codificată şi reprezentată printr-un anumit număr de octeţi ce poartă denumirea de codul maşină al instrucţiunii. Deci codurile instrucţiunilor direct executabile de către microprocesor nu sunt altceva decât numere binare care sunt preluate din memoria sistemului. Fiecare cod declanşează, după decodificarea sa în circuitul de comandă al microprocesorului, o serie de activităţi ce converg spre efectuarea acelei instrucţiuni. Astfel că procesorul vede un program ca o înşiruire de octeţi plasaţi în memorie începând cu o anumită adresă.

Exemplul 3.1: În continuare se vor prezenta modurile de codificare pentru câteva instrucţiuni.

|

Mnemonica Z80 |

Codul obiect |

Exemplu |

Observaţii |

| LD r, r’ | 01 r r’ |

LD C,A - 01001111b (4Fh) |

- codificarea registrelor este prezentată în Tabelul 3.2. |

| LD r, n |

00 r 110 n |

LD B, 3ah - 00000110b (06h) - 00111010b (3ah) |

- instrucţiunea are doi octeţi dintre care primul este codul instrucţiunii iar al doilea operandul cu adresare imediată; - citirea primului octet din memorie se face printr-un ciclu de fetch iar citirea operandului printr-un ciclu de citire. |

| LD (IX+d), r |

11011101 01110 r d |

LD (IX+10), L - 11011101b (DDh) - 01110101b (75h) - 00001010b (0ah) |

- procesorul execută două cicluri de fetch pentru citirea primilor doi octeţi; apoi execută un ciclu de citire pentru operand şi un ciclu de scriere a rezultatului în memorie. |

| LD dd, nn |

00dd0001 n n |

LD DE, 4000h - 00010001b (11h) - 00000000b (00h) - 01000000b (40h) |

- codificarea registrelor duble este prezentată în tabelul 3.3; - operanzii reprezentaţi pe doi octeţi se plasează în memorie cu octetul mai puţin semnificativ la adresa mai mică. |

| BIT b, r |

11001011 01 b r |

BIT 3, A - 11001011b (CBh) - 01011111b (5Fh) |

- bitul testat se codifică pe trei biţi. |

| JP nn |

11000011 n n |

JP 4000h - 11000011b (C3h) - 00000000b (00h) - 01000000b (40h) |

- adresa absolută se plasează în memorie începând cu octetul mai puţin semnificativ. |

| JR e |

00011000 e - 2 |

JR 10

- 00011000b (18h) - 00001000b (08h) JR -4 - 00011000b (18h) - 11110110b (F6h) |

- octetul operand conţine adresa relativă faţă de PC-ul instrucţiunii următoare (e-2) iar e este relativ la PC-ul instrucţiunii JR; - slaturile se pot face în domeniul (-128, +127) faţă de PC-ul instrucţiunii următoare celei de JR sau (-126, +129) faţă de PC-ul instrucţiunii JR; - în cazul salturilor înainte operandul instrucţiunii conţine numărul de octeţi peste care se sare; - în cazul salturilor înapoi operandul conţine un număr negativ reprezentat în complement faţă de 2, şi reprezintă tot numărul de octeţi peste care se face saltul. |

Tabelul 3.1

|

r, r’ |

Registre |

dd |

Registre |

|

|

000 |

B |

00 |

BC |

|

|

001 |

C |

01 |

DE |

|

|

010 |

D |

10 |

HL |

|

|

011 |

E |

11 |

SP |

|

|

100 |

H |

|||

|

101 |

L |

|||

|

111 |

A |

|||

Tabelele 3.2 şi 3.3

Instrucţiunile microprocesorului Z80 pot ocupa în memorie 1, 2, 3 sau 4 octeţi în următoarele combinaţii posibile:

|

Număr de octeţi/ instrucţiune |

Combinaţii posibile |

Exemple |

|

1 octet |

1 octet de cod |

LD D, H |

|

2 octeţi |

1 octet de cod + 1 octet de date |

LD H, 37h |

|

2 octeţi de cod |

LDI |

|

|

3 octeţi |

1 octet de cod + 2 octeţi de date |

LD BC, 4000h |

|

2 octeţi de cod + 1 octet de date |

LD A, (IX+10) |

|

|

4 octeţi |

2 octeti de cod + 2 octeţi de date |

LD IX, 1000h |

|

3 octeţi de cod + 1 octet de date |

BIT 3, (IY+5) |

Tabelul 3.4

Deoarece programarea la nivel de cod maşină este dificilă se foloseşte programarea la nivel de limbaj de asamblare. Codurile instrucţiunilor se formulează în limbajul de asamblare ca şi cuvinte cheie care exprimă funcţia reprezentată de codul respectiv. Aceste cuvinte cheie se numesc mnemonici.

Limbajul de asamblare este o imagine fidelă a setului de instrucţiuni, el exprimând cât se poate de exact operaţiile elementare pe care o unitate centrală de microprocesor le poate executa. În plus faţă de setul de instrucţiuni, un limbaj de asamblare mai oferă posibilitatea de definire a variabilelor, constantelor şi introducerea unor directive de asamblare.

Între instrucţiunile limbajului de asamblare şi codurile binare de instrucţiuni (codurile maşină) ale unui procesor există totdeauna o relaţie biunivocă: fiecărei instrucţiuni în limbaj de asamblare îi corespunde unul şi numai un cod.

O secvenţă de program scris în limbaj de asamblare respectiv codul maşină asociat este următoarea:

Exemplul 3.2:limbaj asamblare cod maşină

Formatul general al unei instrucţiuni în limbaj de asamblare este următorul:

MNEMONICĂ [operand 1, [operand 2]]

Programul care realizează translatarea din limbajul de asamblare în codul maşină corespunzător se numeşte asamblor. Sintaxa completă a unei linii de cod recunoscută de asamblor (dependentă de asamblor) este prezentată mai jos:

ETICHETĂ: MNEMONICĂ operand_destinaţie, operand_sursă ; comentariu

iar pentru definirea unei variabile şi respectiv a unei constante sintaxa este:

ETICHETĂ: CAPACITATE secvenţa_de_iniţializare ; comentariu

ETICHETĂ EQU VALOARE

unde avem:

Exemplul 3.3:

Pentru ca un program (ciclurile maşină ale programului) să poată fi vizualizat cu osciloscopul trebuie să îndeplinească următoarele două proprietăţi:

Monitorul este un program ce oferă un set minim de operaţii utile la exploatarea microsistemului.

Câteva dintre comenzile acceptate sunt următoarele:

XXXX – număr hexa.

În cadrul laboratorului se vor parcurge următorii paşi: