În cadrul acestei lucrări se va prezenta interfaţa serială bazată pe circuitul 8250.

Prin interfaţa serială se înţelege ansamblul circuitelor şi programelor de bază care asigură comunicaţia între unitatea centrală (procesor) şi un dispozitiv periferic care transferă informaşia bit după bit.

Interfaţa serie se foloseşte atunci când distanţa de comunicaţie este mare (> 1.50 m). Pe distanţe mari riscul de perturbare a informaţiei este mare; cu cât numărul de linii este mai mic cu atât posibilitatea de perturbare scade.

Vitezele de transfer pe linie au fost standardizate, există anumite trepte de viteză bine determinate. Unitatea de măsură a vitezei de transfer pe liniile seriale este 1 baud = 1 bit/sec.

Transferul serie este de trei tipuri:

- simplex

- semiduplex

- dulpex

Din punctul de vedere al organizării comunicaţia serială poate fi:

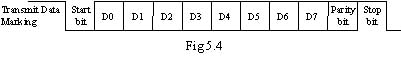

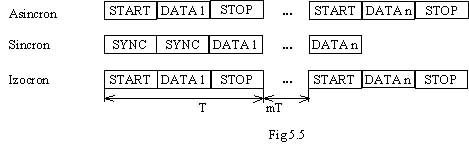

- asincronă - caracterizată prin transferul unui caracter la un moment dat. Când pe linia de comunicaţie nu circulă informaţii ea este în starea inactivă (“1”). În momentul în care emiţătorul doreşte să transfere un caracter el începe prin activarea la “0” a liniei pentru o perioadă corespunzătoare cu durata unui bit. Acest bit de “0” are rol de start şi foloseşte la sincronizarea receptorului. Receptorul testează în permanenşă linia iar în momentul în care sesizează apariţia unui “0” repetă testul după o durată egală cu 1/2 din durata unui bit. Dacă regăseşte linia pe “0” consideră că acesta este bitul de start şi în continuare citeşte linia cu o perioadă egală cu durata unui bit. Deci receptorul va citi bişii de pe linie la aproximativ 1/2 din durata lor. Transmiţătorul după ce a plasat bitul de start, plasează rangurile de date după care plasează un eventual rang opţional de paritate după care transferul se încheie prin plasarea pe linie a 1, 1 1/2 sau 2 biţi de stop (“1”).

- sincronă - constă în transferul datelor fără informaţia de cadrare, dar numai sub formă de blocuri şi precedate de 1-5 octeţi de sincronizare. Octeţii de sincronizare au rolul pe care îl are bitul de start de la transferul asincron. Receptorul citeşte linia, asamblează informaţia ce soseşte pe linie şi compară caracterul sosit cu cel de sincronizare, pe care-l ştie din faza de programare. Dacă au fost identificaşi octeţii de sincronizare se vor prelua în continuare datele. Datele pleacă pe linie cu cadenţă fixă dată de un tact. Şi aici emiţătorul poate începe o transmisie când doreşte, dar trebuie să transmită tot blocul de date.

- izocronă - fiecare caracter are informaţia de cadrare, dar distanţa în timp dintre două caractere succesive trebuie să fie un multiplu al duratei unui caracter.

8250 este un circuit specializat pentru realizarea comunicţiilor seriale. Circuitul este programabil şi suportă doar modul de comunicaţie asincron. Acesta va adăuga biţii de start, biţii de stop şi cei de control al parităţii. Viteza de comunicaţie este programabilă şi este cuprinsă între 50 baud şi 9600 baud. Lungimea cuvântului este şi ea programabilă şi poate fi de 5, 6, 7 sau 8 biţi cu 1, 1 1/2 sau 2 biţi de stop.

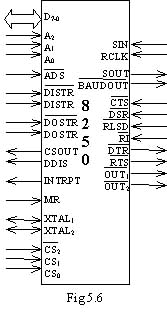

CS0, CS1, /CS2 (Chip Select) - când CS0 = CS1 = 1 şi /CS2 = 0, circuitul este selectat. Selectarea circuitului este completă atunci când semnalul de selecţie de la decodificator este însoţit de un semnal /ADS (Address Strobe) activ pe 0. Acesta permite comunicarea între 8250 şi procesor.

DISTR, /DISTR (Data Input Strobe) - dacă semnalele sunt active în timp ce circuitul este selectat are loc citirea informaţiei din registrul de stare sau a unei date din registrul selectat. Numai una din cele două intrări trebuie să fie activă la un moment dat.

DOSTR, /DOSTR (Data Output Strobe) - când unul dintre semnale este activ şi circuitul este selectat procesorul poate înscrie o dată sau un cuvânt de comandă în registrul selectat.

/ADS (Address Strobe)

A0, A1, A2 (Register Select) - intrări pentru selecţia registrelor.

|

DLAB |

A2 |

A1 |

A0 |

Register |

|

0 |

0 |

0 |

0 |

Receiver Buffer (Read)/ Transmitter Holding Register (Write) |

|

0 |

0 |

0 |

1 |

Interrupt Enable |

|

x |

0 |

1 |

0 |

Interrupt Identification Register (Read Only) |

|

x |

0 |

1 |

1 |

Line Control |

|

x |

1 |

0 |

0 |

Modem Control |

|

x |

1 |

0 |

1 |

Line Status |

|

x |

1 |

1 |

0 |

Modem Status |

|

x |

1 |

1 |

1 |

None |

|

1 |

0 |

0 |

0 |

Divisor Latch (Least Significant Byte) |

|

1 |

0 |

0 |

1 |

Divisor Latch (Most Significant Byte) |

Tabelul 5.1

MR (Master Reset) - intrare de reset. Când este activă şterge toate registrele cu excepţia registrelor de recepţie şi a celor de divizare.

RCLK (Receiver Clock) - intrare de tact pentru recepţie (este 16*rata de transfer).

SIN (Serial Input) - intrare de date de pe linia serială.

/CTS (Clear to Send) - linie de contro în comunicaţia cu modemul.

/DSR (Data Set Ready) - linie de contro în comunicaţia cu modemul.

/RLSD (Received Line Signal Detect) - linie de control în comunicaţia cu modemul.

/RI (Ring Indicator) -

/DTR (Data Terminal Ready) -

/RTS (Request to Send) -

/OUT1, /OUT2 (Output) -

CSOUT (Chip Select Out) - este răspunsul circuitului la o activare a semnalelor CS0, CS1, /CS2. Nu se poate face nici un transfer cu 8250 până când acest semnal nu este activat.

DDIS (Driver Disable) - acest semnal este pus pe 0 când procesorul citeşte date de la circuitul 8250. El poate fi utilizat pentru comanda unui transceiver, dacă există pe magistrala de date între procesor şi 8250.

/BAUDOUT (Baud Out) - semnal de tact pentru transmisie.

INTRPT (Interrupt) - semnal activ pe 1 şi lansează o cerere de întrerupere l procesor când apare unul din următoarele evenimente: eroare la recepţie, dată recepţionată disponibilă, buffer de transmisie gol, modificare stare modem.

SOUT (Serial Output) - linie de transmisie serială de date.

D0-D7 (Data) - linii de conectare la magistrala de date.

XTAL1, XTAL2 (External Clock Input/Output) - intrări pentru semnal de tact extern.

Procesorul poate avea acces la oricare din registrele circuitului 8250.

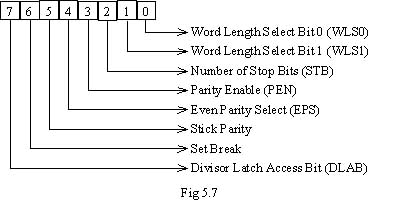

Registrul de control (Line Control Register)

Biţii 1 şi 0 indică lungimea caracterului transmis:

|

WLS1 |

WLS0 |

Lungimea caracterului |

|

0 |

0 |

5 Biţi |

|

0 |

1 |

6 Biţi |

|

1 |

0 |

7 Biţi |

|

1 |

1 |

8 Biţi |

Tabelul 5.2

Bitul 2 indică numărul de biţi de stop:

Bitul 3 indică dacă se foloseşte sau nu un bit de paritate în transmisie sau recepţie.

Bitul 4 selectează tipul de paritate.

Bitul 5 - dacă bitul 3 este pe “1” şi bitul 5 este tot pe “1” atunci bitul de paritate este transmis şi este detectat la recepţie ca “0” dacă EPS=1 sau ca şi “1” dacă EPS=0.

Bitul 6 - set break control bit. Când este pe “1”, linia de ieşire serială (SOUT) este forşată pe “0” şi rămâne aşa indiferent de aparişia altor activităţi de tramsmisie. Această stare este dezactivată prin punerea acestui bit pe “0”. Această caracteristică permite procesorului să alerteze un terminal într-un sistem de comunicaţie.

Bitul 7 este bitul de acces la registrul pentru divizarea ratei:

Registrele de divizare

Generatorul ratei de transfer preia tactul de intrare şi îl împarte cu orice număr cuprins între 1 şi 216 - 1, număr aflat în registrele de divizare. Frecvenţa de ieşire a generatorului este 16x rata.

divisor = (frecvenţa de intrare) / (baud rate x 16)

Numărul cu care se divide tactul este stocat în două registre, care se încarcă în timpul iniţializării, cu valorile corespunzătoare ratei de transfer dorite.

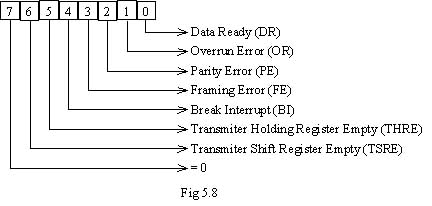

Registrul de stare

Bitul 0 = 1 - s-a recepţionat un caracter şi a fost transferat în buffer-ul de recepţie.

Bitul 1 = 1 - indică faptul că data din buffer-ul de recepţie nu a fost citită de către procesor înaintea recepţionării unui alt caracter. Astfel că acest prim cuvânt a fost pierdut. Bitul OE este pus pe 0 la citirea registrului de stare de către procesor.

Bitul 2 - indică apariţia unei erori de paritate.

Bitul 3 - apariţia unei erori de cadru. Caracterul recepţionat nu are bitul de stop valid. Acest bit este pus pe 1 de fiecare dată când bitul de stop ce urmează după ultimul bit de date sau după bitul de paritate, este 0.

Bitul 4 - indică dacă linia de recepţie este în starea 0 o perioadă de timp mai mare decât timpul necesar transmisiei complete a unui caracter. Înseamnă că transmiţătorul a forţat linia pe 0 (Set Break).

Bitul 5 - indică procesorului că 8250 este pregătit pentru a primi un nou caracter ce trebuie transmis. Acest bit este setat la “1” când un caracter este transferat din buffer-ul de transmisie în registrul de serializare. Bitul este resetat la “0” când procesorul încarcă buffer-ul de transmisie cu un nou caracter.

Bitul 6 - indică faptul că registrul de serializare este gol. Bitul este pus pe “0” odată cu încărcare unui nou caracter din buffer-ul de transmisie.

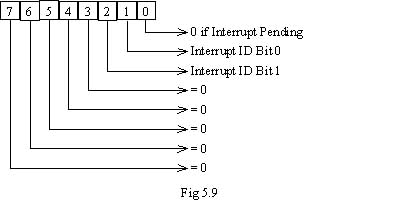

Registrul de identificare a întreruperii

Modul de lucru al circuitul 8250 cu întreruperile oferă o flexibilitate ridicată şi permite interfaţarea lui cu aproape toate procesoarele cunoscute. Pentru a minimiza încărcarea programului de comunicaţie serială, 8250 realizează o prioritizare a întreruperilor în patru nivele:

Când acest registru este citit de către procesor el indică doar cererea de întrerupere cea mai prioritară care este în aşteptare şi numai după ce a fost satisfăcută această cerere el va indica şi celelalte cereri ce aşteaptă dar care au nivel de prioritate mai mic.

Dacă bitul 0 este pe “1” nici o cerere de întrerupere nu este în aşteptare.

|

Bitul 2 |

Bitul 1 |

Bitul 0 |

Nivel de prioritate |

Tipul întreruperii |

Sursa întreruperii |

ªtergerea întreruperii |

|

0 |

0 |

1 |

- |

- |

- |

- |

|

1 |

1 |

0 |

1 |

Starea liniei la recepţie |

Eroare de ritm Eroare de paritate Eroare de cadrare Break interrupt |

Citirea registrului de stare |

|

1 |

0 |

0 |

2 |

Caracter recepţionat disponibil |

Caracter recepţionat disponibil |

Citirea buffer-ului de recepţie |

|

0 |

1 |

0 |

3 |

Buffer de transmisie gol |

Buffer de transmisie gol |

Citirea IIR sau Scrierea unui nou caracter în buffer-ul de transmisie |

|

0 |

0 |

0 |

4 |

Stare modem |

Clear to Send Data Set Ready Ring Indicator Received Line Signal Detect |

Citirea registrului de stare pentru modem |

Tabelul 5.3

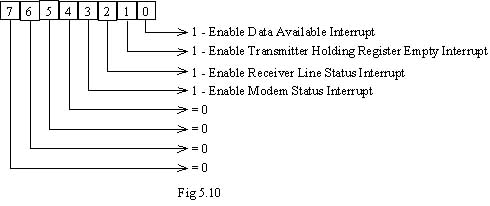

Registrul de validare a intreruperilor

Acest registru permite ca cele patru surse de întrerupere să activeze separat linia de cerere de întrerupere INTRPT. Sistemul de întreruperi se poate dezactiva prin resetarea biţilor 3-0 ai acestui registru.

În cadrul laboratorului se va realiza interfaţarea sistemului cu microprocesorul Z80 cu un terminal prin intermediul interfeţei seriale. Pentru aceasta se vor realiza: