Simularea unui design utilizand Modelsim

Aceasta prezentare descrie modul de utilizare a mediului Modelsim pentru proiectarea si simularea modulelor Verilog. Unitatea implementata in acest exemplu este un design combinational prevazut cu o intrare, x, pe 8 linii si o iesire, y. Iesirea este activa avand valoarea 1 cand cifra sutelor a numarului intreg fara semn furnizat la intrare are valoarea 2.

Exemplu: Pentru configuratia binara '11001001' (valoarea 201 in configuratie binara fara semn) aplicata la intrare, iesirea are valoarea 1 iar pentru configuratia binara de intrare '00001100' iesirea are valoarea 0.

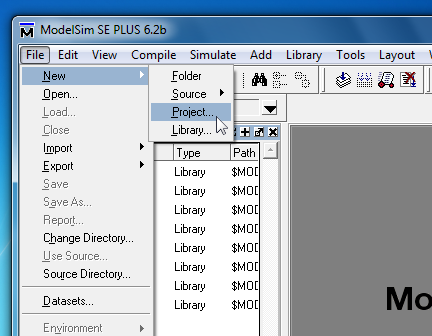

Crearea unui proiect in Modelsim

Se alege meniul File -> New -> Project.

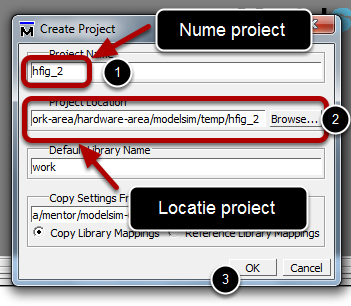

Selectarea locatiei si a numelui proiectului

Se alege un nume pentru proiect si se selecteaza locatia in care va fi salvat. Se apasa OK.

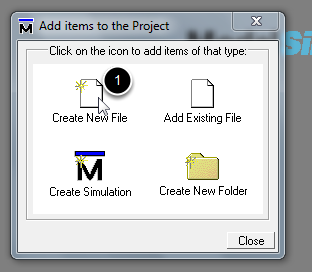

Adaugarea unui fisier la proiect

Se apasa "Create New File".

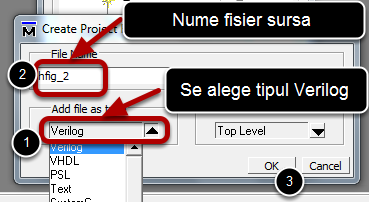

Crearea unui fisier sursa Verilog

Se selecteaza tipul fisierului sursa ca fiind Verilog. Se alege un nume (dupa selectarea tipul de fisier sursa ca Verilog nu se va adauga extensie numelui de fisier). Se apasa OK.

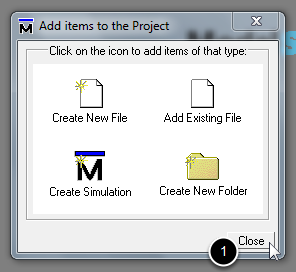

Inchiderea fereastrei "Add items to the Project"

Se apasa Close.

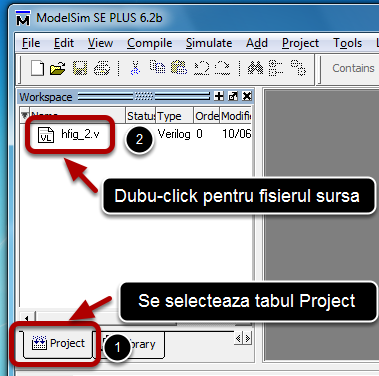

Deschiderea unui fisier sursa pentru editare

Se selecteaza tabul Project (daca acesta nu este vizibil se va activa din meniul View -> Workspace). Se efectueaza dublu-click pentru a deschide fisierul sursa pentru in vederea editarii.

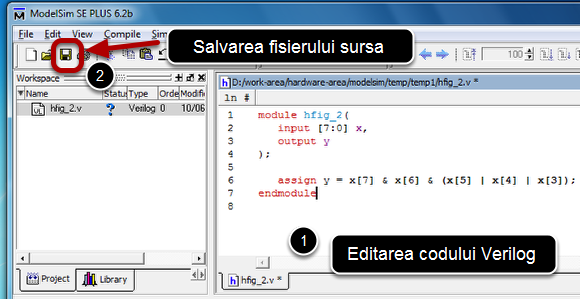

Editarea fisierului sursa

Se editeaza codul Verilog ca in figura. Se salveaza fisierul sursa.

Important: Este esentiala salvarea codului sursa inainte de compilarea acestuia!

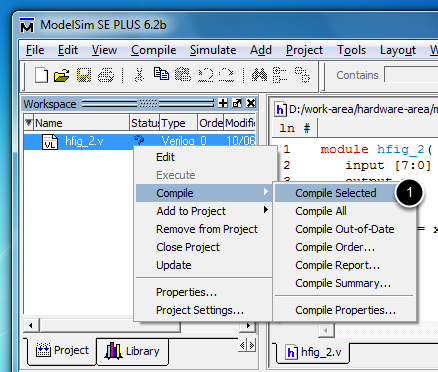

Cmpilarea descrierii Verilog

Se face click-dreapta pe fisierul sursa in tabul Project si se alege meniul Compile -> Compile Selected.

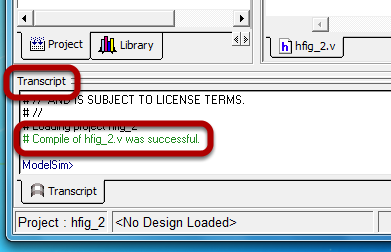

Verificarea compilarii cu succes in fereastra Transcript

Daca au aparut erori in procesul de compilare se efectueaza dublu-click pe linia de eroare (marcata cu culoare rosie) in fereastra Transcript pentru a deschide un raport de compilare indicand posibilele cauze ale erorii. Daca nu au fost intampinare erori la compilare este afisat mesajul de compilare cu succes in fereastra Transcript ca in figura.

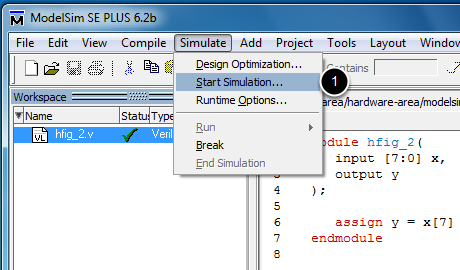

Pornirea simularii

Se alege meniul Simulate -> Start Simulation.

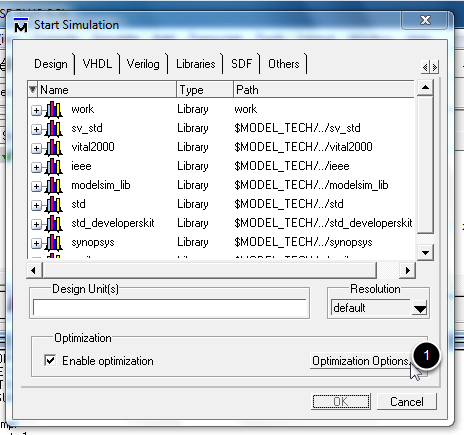

Modificarea optiunilor de optimizare a simularii

Se apasa butonul "Optimization Options".

Important: Este esentiala pornirea simularii in modul prezentat in vederea depanarii ulterioare design-ului! Exista si posibilitatea de demarare a simularii din linia de comanda a ferestrei transcript.

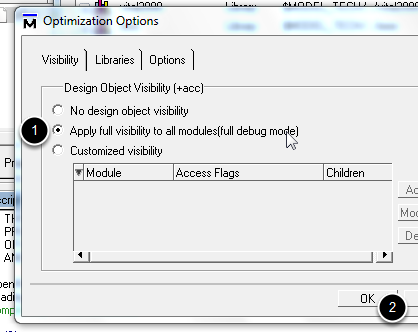

Alegerea modului de vizibilitate completa

Se alege optiunea "Apply full visibility to all modules(full debug mode)". Se apasa OK.

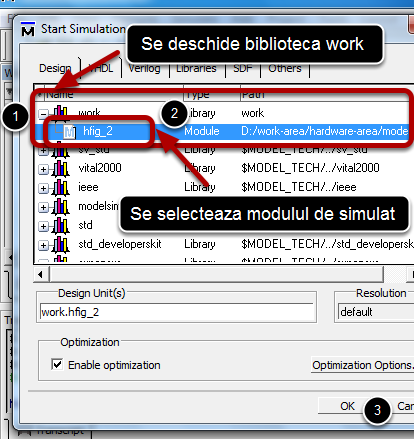

Selectarea modulului de simulat

Se deschide biblioteca work (din tabul Design). Se selecteaza modulul de simulat. Se apasa OK.

Important: elementele bibliotecii work poarta numele modulelor definite in fiserele sursa si nu numele fisierelor sursa continand modulele in cauza. Consecinta: fisierul sursa al unui modul va fi salvat sub acelasi nume cu al modulului descrise in acesta!

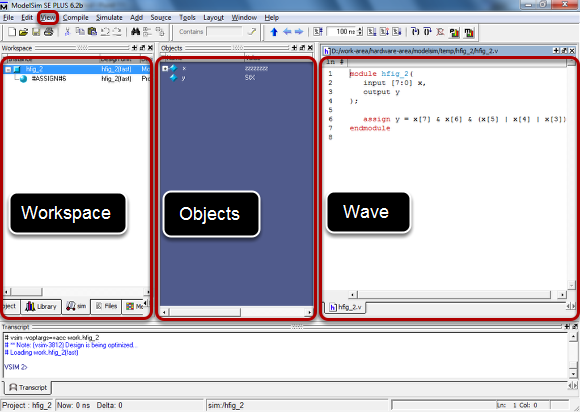

Configuratia de simulare a mediului Modelsim

Urmatoarele ferestre sunt necesare pentru simularea unui design: Workspace (deschisa din meniul View -> Workspace), Objects (deschisa din meniul View -> Objects) si Wave (deschisa din meniul View -> Wave).

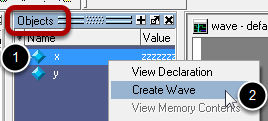

Crearea formelor de unda pentru intrari

Pentru toate intrarile (in cazul problemei curente pentru singurul semnal de intrare, x, pe 8 biti) se creaza o forma de unda prin efectuarea clik-dreapta in dreptul numelui semnalului de intrare vizat in fereastra Objects si selectarea meniului "Create Wave".

Configurarea formelor de unda

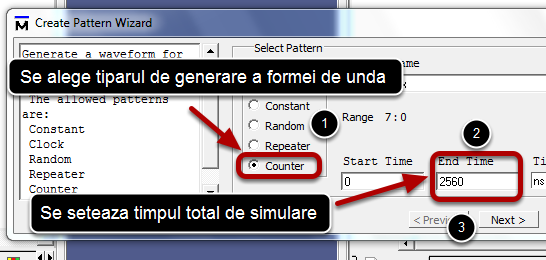

Se genereaza forma de unda potrivit specificatiilor designului implementat.

Pentru problema curenta sunt alese toate configuratiile binare de intrare reprezentand numere zecimale intre 0 si 255 pentru a fi aplicate la intrarea x (se au in vedere atat configuratii de intrare care genereaza 0 cat si toate configuratiile care determina iesirea 1). Fiecare configuratie va fi activa la intrare timp de 10 ns. Intrucat vor fi simulate in total 256 de configuratii de intrare, timpul total de simulare este de 2560 ns. Configuratiile de intrare vor fi generate secvential utilizand tiparul de generare Counter.

Potrivit consideratiilor prezentate se configureaza forma de unda potrivit imaginii alaturate. Se alege Next.

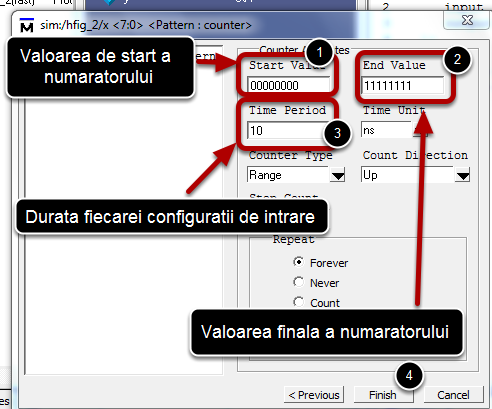

Configurarea formelor de unda (continuare)

Se seteaza valoarea initiala si finala a numaratorului ca in figura (valoarea de start 0 are configuratia binara 00000000, iar valoarea finala a secventei, 255 are configuratia binara 11111111). Se seteaza de asemenea durata fiecarei configuratii, care va avea valoare 10 ns potrivit cu consideratiile pasului anterios. Se apasa butonul Finish.

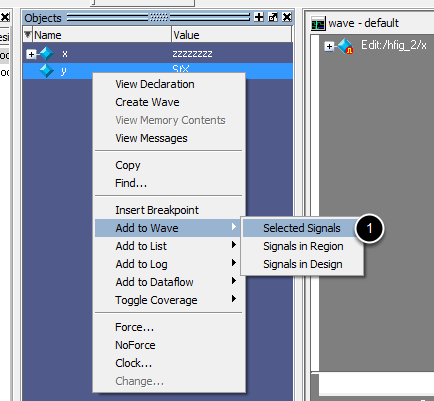

Adaugarea iesirilor in fereastra formelor de unda

Formele de unda create pentru intrari sunt adaugate implicit in fereastra formelor de unda.

Fiecare iesire din design se adauga la fereastra formelor de unda prin efectuarea click-dreapta in dreptul semnalului de iesire vizat din fereastra Objects si alegerea meniului Add to Wave -> Selected Signal. Se adauga in modul acesta iesirea y la fereastra formelor de unda.

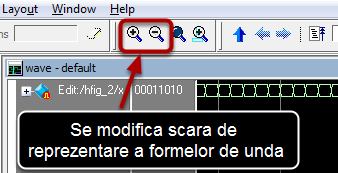

Configurarea ferestrei formelor de unda

Se modifica scara de reprezentare a formelor de unda folosind butoanele indicate pentru a permite vizualizarea corespunzatoare a configuratiilor binare de analizat.

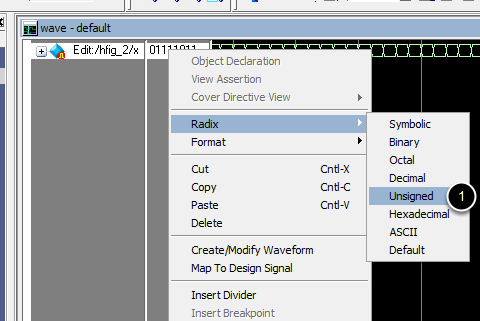

Ajustarea bazei sistemului de numeratie in reprezentarea formelor de unda

Pentru fiecare semnal necesitand modificarea bazei de numeratie se efectueaza click-dreapta in dreptul semnalului vizat in fereastra Wave si se alege baza din meniul Radix, surprins in imaginea alaturata.

Pentru problema curenta, pentru ca intrarea x reprezinta un numar intreg fara semn, modificarea de baza pentru x presupune alegerea meniului Radix->Unsigned.

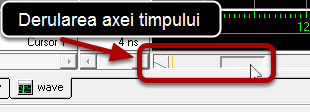

Derularea axei timpului spre momentul initial al simularii

Se deruleaza axa timpului spre inceputul simularii.

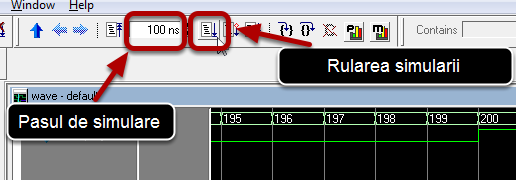

Rularea simularii

Se ruleaza simularea in mod repetat pentru toate configuratiile de intrare.

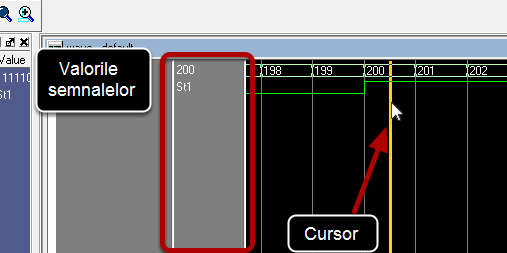

Inspectarea corectitudinii iesirilor

La efectuarea unui click in fereastra Wave se pozitioneaza automat un cursor de timp (de culoare galbena) in dreptul momentului de timp selectat. Valorile semnalelor din fereastra formelor de unda de la momentul indicat de cursor sunt surprinse in zona marcata pe figura alaturata. se inspecteaza corectitudinea implementarii deruland axa timpului pentru analiza configuratiilor relevante.

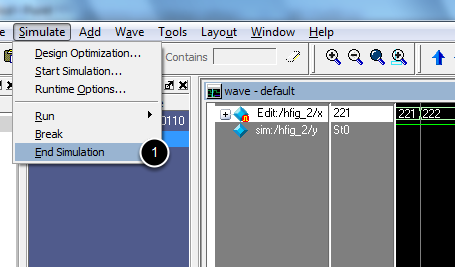

Oprirea simularii

Simularea este oprita din meniul Simulate -> End Simulation.

Important: Inaintea modificarii si recompilarii unui design simularea curenta trebuie oprita!

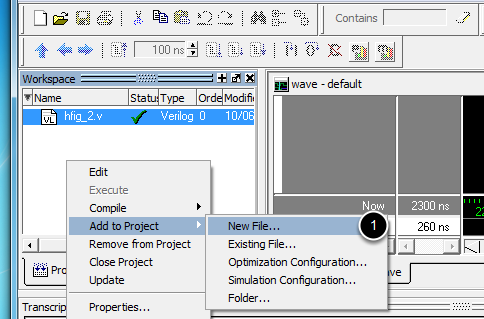

Adaugarea altor fisiere sursa la proiect

In tabul Project tab a ferestrei Workspace se efectueaza click-dreapta intr-o zona goala a tab-ului si se selecteaza meniul Add to Project -> New File...

Vor fi respectate in continuare consideratiile pasului 4 de crearea a unui fisier sursa Verilog.